Вишејезгарни процесор

Вишејезгарни процесор је једна рачунарска компоненета са две или више независних стварних централних процесорских јединица (названих “језгра”), а те јединице читају и извршавају програмске инструкције. [тражи се извор] Инструкције су обичне CPU инструкције као сабирање, покретање података и гранање, али вишејезгарни процесори могу да извршавају више инструкција у исто време, повећањем укупне брзине за програме који подлежу паралелном рачунању.[тражи се извор] Произвођачи обично интегришу језгра на једно интегрисано коло (познато као вишепроцесорски чип или CMP), или на више чипова унутар једног паковања чипа.

Процесори су се првобитно развили само са једним језгром. Двојезгарни (Dual-core) процесор има два језгра (нпр. AMD Phenom II X2, Intel Core Duo), quad-core процесор садржи четири језгра (нпр. AMD Phenom II X4, Intel-ов quad-core процесор, види i5 и i7 на Intel Core), 6- core процесор садржи шест језгара (нпр. AMD Phenom II X6, Intel Core i7 Extreme Edition 980X), 8-core процесор садржи осам језгара (нпр. Intel Xeon E7-2820, AMD FX-8350), 10-core садржи десет језгара (нпр. Intel Xeon E7-2850), 12-core процесор садржи дванаест језгара. Вишејезгарни процесор имплементира мултипроцесовање на једном физичком паковању. Дизајнери могу упарити језгра у вишејезгарни уређај чврсто или лабаво. На пример, језгра могу или не могу делити кеш, и они могу да имплементирају преношење поруке или дељење меморије унутар језгара комуникационих метода. Заједничка мрежа топологије која повезује језгара укључује магистралу, прстен, дводимензионалну мрежу и crossbar. Хомогени вишејезгарни системи укључују само идентична језгра, хетерогени вишејезгарни системи имају језгра која нису идентична. Као и код јено-процесорског система, језгра у вишејезгарним системима могу имплементирати архитектуру такву као суперскаларну, VLIW, векторску обраду, SIMD или вишенитно.

Вишејезгарни процесори имају широку употребу у многим областима примене, укључујући општу намену, уграђеност, мреже, дигиталну обрада сигнала (DSP) и графику.

Побољшање перформанси добијено коришћењем вишејезгарног процесора доста зависи од коришћених алгоритама софтвера и њихове имплементације. Посебно, могући добици су ограничени од делова софтвера који се могу извршавати паралелно истовремено на више језгара; овај ефекат се описује помоћу Amdahl-овог закона. У најбољем случају, такозвани паралелни неометани проблеми могу реализовати факторе убрзања близу бројних језгара, али још више ако је проблем довољно подељен да може стати у сваки кешов кеш, чиме се избегава коришћење много спорије главне меморије. Већина апликација, мађутим, неће се значајно убрзати сем ако програмер уложи довољну количину напора у поновно рефакторисање проблема.[1] Паралелизација софтвера је значајна тема у току истраживања.

Терминологија уреди

| Број језгара | Уобичајено име |

|---|---|

| 1 | single-core |

| 2 | dual-core |

| 3 | tri-core triple-core |

| 4 | quad-core |

| 5 | penta-core |

| 6 | hexa-core |

| 7 | hepta-core |

| 8 | octa-core, octo-core |

| 9 | nona-core |

| 10 | deca-core |

| 11 | hendeca-core |

| 12 | dodeca-core |

| 13 | trideca-core |

| 14 | tetradeca-core |

| 15 | pentadeca-core |

| 16 | hexadeca-core |

| 17 | heptadeca-core |

| 18 | octadeca-core |

| 19 | enneadeca-core |

| 20 | icosa-core |

Термин вишејезгарни или двојезгарни углавном се односи на неку врсту централне процесорске јединице (CPU), али се понекад такође примењује и на процесоре дигиталних сигнала (DSP) и систем-на-чипу (SoC). Термин се обично користи само да упути на вишејезгарне микропроцесоре који су произведени на истом чипу интегрисаног кола; одвојени микропроцесорски чипови на истом пакету се обично називају другим именом, као више-чиповни модули. Овај чланак користи термине “вишејезгарни” и “двојезгарни” за CPU производњу на истом интегрисаном колу, осим ако није другачије речено.

За разлику од вишејезгарних система, термин multi-CPU се односи на више физички раздвојених процесорских јединица (које често садрже посебна кола да олакшају мођусобну комуникацију).

Термини many-core и massively multi-core се понекад користе да се опише вишејезгарна архитектура са посебно великим бројем језгара (десетине или стотине).[2]

Неки системи користе доста меких микропроцесорских језгара постављених на један FPGA. Свако “језгро” може се сматрати као "semiconductor intellectual property core" (полупроводничка интелектуална својина језгра) као и CPU језгро.

Развој уреди

Док се технологија производње побољшава, смањење величина индивидуалних капија, физичка ограничења микроуређаја базираних на полупроводницима су постала важна дизајнерска брига. Ова физичка ограничења могу проузроковати значајно расипање топлоте и пробелма у синхронизацији података. Разне друге методе се користе за побољшање CPU перформанси. Неки instruction-level parallelism (ILP) (инструкциони нивои паралелизма) као суперскаларни pipeline је погодан за многе апликације, али није ефикасан за оне које садрже код тежак-за-предвиђање. Многим апликацијама више одговара метод паралелизма на нивоу нити (TLP), и више независних CPU се обично користи за убрзање система. Комбинација повећаног расположивог простора (због префињених процеса производње) и повећана потражња за TLP довела је до развоја вишејезгарних процесора.

Комерцијални подстицаји уреди

Неколико пословних мотива довело је до развоја двојезгарне архитектуре. Деценијама, било је могуће повећавати перформансе процесора помоћу смањења простора између интегрисаних кола, који је оборио цену по урађају на IC. Алтернативно, за исту површину кола, могло је више транзистора да се употреби у дизајну, што је повећало функционалност, посебно за CISC архитектуру. Такт је такође порастао за редове величине у деценијама крајем 20. века, од неколико мегахерца и 1980. године на неколико гигахетца и раним 2000-им годинама.

Док се вредност брзине генератора такта побољшавала успорено, повећавала се употреба паралелног израчунавања у облику вишејезгарних процесора који су тежили да побољшају укупне перформансе обраде. Више језгара се користило на истом CPU чипу, који онда може да доведе до боље продаје CPU чипова са два или више језгара. Intel је произвео процесор са 48 језгара за истраживање у облаку; свако језгро је имало Х86 архитектуру.[3] Intel је оптеретио Linux на свако језгро.[4]

Технички фактори уреди

Пошто су произвођачи рачунара дуго имплементирали симетричан мултипроцесорски (SMP) дизајн коришћењем дискретних процесора, питања у вези имплементирања вишејезгарне архитектуре и њеног подржавања са софтвером су добро позната.

Додатно:

- Употреба доказаних процесорских језгара без промена архитектуре значајно смањују дизајнерски ризик.

- За процесоре опште намене, велики део мотивације за вишејезгарни процесор долази из веома смањеног добитка у перформансама процесора са повећањем радне фреквенце. То је због три основна фактора:

- #Меморијски зид; повећање у разлици перформанси између процесора и меморије. Овај ефекат гура величине кеша у ред да би се маскирала латенција меморије. Ово помаже само у мери да меморијски опсег није уско грло у перформансама.

- #ILP wall; повећање тешкоће проналажења довољних паралелизама у једном инструкцијском стриму да задржи високо-перформансни једнојезгарни процесор заузетим.

- #power wall; тренд трошења експоненецијалног повећања снаге са сваким факторијалним повећањем радне фреквенције. Ово повећање може се постићи “сужавањем” процесора коришћењем мањих трагова за исту логику. Роwer wall представља производњу, системски дизаин и развојни проблеми који нису били у светлу мањег добитка у перформансама због меморијског зида и ILP wall.

Да бу наставили ипоруку редовног побољшања перформансама за процесоре опште намене, произвођачи као што су Intel and AMD окренули су се ка вишејезгарном дизајну, жртвујући мању цену производње за веће перформансе у неким апликацијама и системима. Вишејезгарна архитектура су развијена, али се развијају и алтернативе. Посебно јак кандидат који ће завладати тржиштем имаће интегрисане периферијске функције на чип.

Предност уреди

Близина више CPU језгара на истом чипу дозвољава да кеш кохеренција кола ради на много већем генераторском такту него што је могуће ако сигнали путују ван чипа. Комбинујући еквивалентне процесоре на једном чипу значајно побољшавамо перфорамнсе кеш snoop (алтернатива: магистрални snooping) операција. Једноставно речено, ово значи да сигнал између различитих процесора прелазе мању раздаљину, па се зато сигнали мање деградирају. Ови сигнали високог квалитета омогућавају слање више података у датом временском периоду, пошто индивидуални сигнали могу бити краћи и не морају да се често понављају.

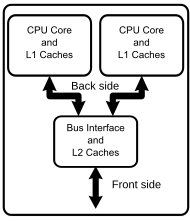

Претпостављајући да чип може стати у једно паковање, физички, вишејезгарни процесорски дизајни захтевају много мање простора за плоче са штампаним колом (PCB) него SMP дизајни са више чипова. Такође, двојезгарни процесор троши мање енергије него два упарена једнојезгарна процесора, углавном због смањене енергије која се захтева за довођење сигнала са споља на чип. Шта више, језгра деле нека кола, као L2 кеш и интерфејс на спољној страни магистрале (front side bus - FSB). У погледу конкурентних технологија за расположиви силицијум на чипу, вишепроцесорски дизајн може да користи доказане CPU језгране библиотеке дизајна и производњу уређаја са мањим ризиком од грешке дизајна него смишљање новог ширег језгарног дизајна. Такође, додавање кеша има мању зараду.

Вишејезгарни чипови омогућавају веће перформансе са мањом енергијом. Ово може бити важан фактор за мобилне уређаје који раде на батерије. Пошто свако језгро у вишејезгарном је генерално енергетски ефикаснеје, чип постаје ефикаснији него ако има једно велико монолитно језгро. Ово омогућава веће перформансе са мење енергије. Изазов писања паралелног кода јасно поништава ову погодност.[5]

Недостаци уреди

Максимизирање коришћења комјутерског ресурса омогућено са вишејезгарним процесором захтева подешавање и у подршци оперативног система (ОС) и у постојећима апликационим софтверима. Такође, могућност вишејезгарног процесора да повећа перформансе апликација зависи од коришћења више нити унутар апликације. Ситуација се побољшава: на пример Valve Corporation's Source engine нуди вишејезгарну подршку,,[6][7] а Crytek се развио сличну технологију за CryEngine 2 који покреће њихову игру, Crysis. Emergent Game Technologies' Gamebryo engine укључује њихову Floodgate технологију,[8] која поједностављује вишејезгарно развијање за играчке платформе. Додатно, Apple Inc.'s OS X, почиње са Mac OS X Snow Leopard, и iOS почиње са iOS 4, имају уграђену вишејезгарну инсталацију названу Grand Central Dispatch.

Интеграција вишејезгарног чипа ствара смањен принос у производњи чипова и они су тежи за топлотно управљање него једнојезгарни чип мање густине. Intel се делимично супротставио првом проблему тако што је направио четворојезгарни дизајн спајањем два двојезгарна на један чип са заједничким кешом, дакле било која два двојезгарна чипа се могу користити, насупрот производњи четири језгра на једном чипу и да се захтева да сва четири раде да би био четворојезгарни. Са архитектонске тачке гледишта, на крају, једино процесорски дизаин може боље да искористи силиконску површину него мултипроцесорска језгра, па опредељени развој овој архитектури може носисти ризик од застаревања. Коначно, сирова снага процесора није једино ограничење за перформансе система. Два процесорска језгра деле исту системску магистралу и моморијски пропусни опсег лимитира стварне предности у перформансама. Потврђено је да ако је једно језгро близу меморијског пропусног опсега, онда ће двострука-језгра дати од 30% до 70% побољшања; ако мемеоријски пропусни опсег није проблем, онда се може очекивати побољшање од 90%; међутим, Amdahl-ов закон чини ову тврдњу сумњивом.[9] Било би могуће да су апликације које користе два процесора у завршном процесу брже на двоструком језгру ако комуникација између процесора није лимитирајући фактор, што би било више него 100%-но побољшање.

Хардвер уреди

Трендови уреди

Општи тренд у развоју прецесора је прешао из дво-, тро-, четворо-, шесто-, осмојезгарни чипови у њима са десетинама или чак стотинама језгара. Поред тога, вишејезгарни чип помешан са мултитредингом, меморијом-на-чипу и наменским хетерогеним језгрима обећавају даље добитке у перформансама и већој ефикасности, посебно у обради мултимедија, препознавања и мрежних апликација. Постоји такође и тренд побољшања енергетске ефикасности кроз фокусирање на потрошњу-по-вату са напредним прецизним-зрном или ултра прецизним управљањем напајања и динамичка волтажа и фреквенционо скалирање (тј. лаптоп рачунари и преносиви медија плејери).

Архитектура уреди

Састав и равнотежа језгара у вишејезгарном процесору показује велику разноврсност. Неке архитектуре користе један дизаин језгра који се константно понавља (“хомогени”), док друге користе мешавину различитих језгара, свако оптимизовано за другачију “хетерогену” улогу.

Чланак “CPU дизајнери раправљају о будућности више језгара” од Rick Merritt, EE Times 2008,[10] укључују ове коментаре:

Chuck Moore [...] је предложио да рачунари треба да буду више попут мобилних телефона, који користе различита специјализована језгара за покретање модуларног софтвера одређеним програмским интерфејс апликацијама на високом нивоу.

[...] Atsushi Hasegawa, виши главни инжињер из Renesas, се генерално слаже. Он је предложио да мобилни телефони користе многа специјализована језгра која раде у спрези су добрим моделом за будући вишејезгарни дизајн.

[...] Anant Agarwal, оснивач и извршни директор за покретање Tilera, заузео је супротни став. Он је рекао да вишејезгарни чипови треба да буду хомегена колекција језгара опште намене да би модел софтвера био једноставан.

Софтверски утицај уреди

Застарела верзија антивирус програма може да створи нову нит за скенирање, док GUI нит чека команду корисника (нпр. прекидање скенирања). У том случају, вишејезгарна архитектура је од мале користи за саму апликацију због једне нити која ради тешке задатке и немогућности да се равномерно распореди на сва језгара. Програмирање правог вишенитног кода често захтева комплексну координацију нити и може лако да створи суптилне и тешке-за-проналажење грешке због преплитања процеса на подацима које деле нити (thread-safety). Због тога, такав код је много тежи за дибаговање него једнонитни код, када он одмара. Био је приметан недостатак мотивације за писање нитних апликација за потрошаче због релативне реткости потражње максималног искоришћена хардвера код потрошача. Иако су вишенитне апликације направиле малу додатну казну за перформансе једнопроцесорских машина, додатну горњу производњу било је тешко оправдати због преваге једнопроцесорских машина. Такође, серијски задаци попут декодирања ентропије кодираних алгоритама који се користе у видео кодецима нису могућа да се паралелизују зато што сваки генерисани резултат служи за помоћ при стварању новог резултата ентропије декодованих алгоритама.

Имајући у виду све већи нагласак на дизаин вишејезгарних чипова, који проистичу из термичких проблема и проблема потрошње енергије даљим значајним повећањем брзине процесорског генератора такта, опсег у којој софтвер може бити вишенитни да искористи предност нових чипова је вероватно највеће ограничење на перформансе рачунара у будућности. Ако програмери не буду у стању да дизајнирају софтвер који може у потпуности да искористи ресурсе омогућене од стране више језгара, онда ће они на крају достићи непремостиву границу у перформансама.

Тржиште телекомуникација је било једно од првих коме је био потребан нови дизајн за паралелно процесирање datapath пакета, јер је постојало брзо усвајање вишејезгарних процесора за datapath и контролни панел. Ови MPUs ће заменити[11] традиционалне мрежне процесоре који су базирани на власничком микро- или пико-коду.

Технике паралелног програмирања могу имати директну корист од вишејезгарног процесора. Неки постојећи модели паралелног програмирања су Cilk Plus, OpenMP, OpenHMPP, FastFlow, Skandium, MPI и Erlang који могу бити коришћени на вишејезгарним платформама. Intel је представио нову апстракцију за C++ паралелизам и назвао је TBB. Други истраживачки напори укључују Codeplay Sieve System, Cray's Chapel, Sun's Fortress и IBM's X10.

Вишејезгарна обрада је такође утицала на способност развоја модерног рачунарског софтвера. Развијачи програмирања у новијим језицима могу пронаћи да њихови модерни језици не подржавају вишејезгарну функционалност. Онда ово захтева употребу нумеричких библиотека за приступ коду написаном у језику C и Fortran, који обављају математичке прорачуне брже од новијих језика као што је C#. Intel-ови MKL и AMD's ACML су написани у овим матерњим језицима и користе предност вишејезгарног процесора. Балансирање оптерећења апликација на процесорима може бити проблематично, нарочито ако имају различите перформансне карактеристике. Постоје различити концептуални модели који се баве проблемима, на пример који користе координацију језика и програмске градње блокова (програмска библиотека и/или функције вишег реда). Сваки блок може имати другачију изворну имплементацију за сваки тип процесора. Кориснички једноставан програм који користи ове апстракције и интелигентни компајлер бирају најбољу имплементацију у зависности од контекста.[12]

Управљање конкурентности стиче главну улогу у развоју паралелених апликација. Основни кораци у пројектовању паралелне апликације су:

- Партиционисање

- Фаза партиционисања у дизајну има за циљ да изложи могућности за паралелно извршавање. Отуда, фокус је на дефинисању великог броја малих задатака с циљем да се добије оно што се назива финогранулирано разлагање проблема.

- Комуникација

- Задаци генерисања помоћу партиционисања су намењени за упоредно извршење али не могу, генерално, да се изврше независно. Обављање израчунавања у једном задатку обично ће захтевати податке везане са другим задатком. Подаци се онда морају пренети између задатака како би се омогућио наставак рачунања. Овај ток информација је дефинисан у фази комуницирања дизајна.

- Нагомилавање

- У трећој фази, развој креће од апстрактног према конкретном. Програмери преиспитују одлуке у фази партиционисања и комуникацији у циљу добијања алгоритма који ће се ефикасно извршавати у некој класи паралелног рачунара. Посебно, програмери разматрају да ли је корисно да се комбинују, или нагомилају, задаци идентификовани у фази партиционисања, како би се смањио број задатака, сваки веће величине. Они такође одређују да ли вреди да се реплицирају подаци и/или обрачунају.

- Мапирање

- У четвртој и последњој фази дизајна паралелних алгоритама, програмери одређују где ће се сваки задатак извршити. Овај проблем мапирања се не јавља код једнопроцесорског система или на рачунарима са дељеном меморијом која обезбеђује аутоматско распоређивање задатака.

С друге стране, са стране сервера, вишејезгарни процесори су идеални зато што омогућавају корисницима да се истовремено повежу на сајту и да имају независне нити за извршавање. Ово омогућава Веб серверима и апликационим серверима да имају много већи проток.

Лиценцирање уреди

Типично, приватни предизеће-сервер софтвер је лиценциран “по процесору”. Када је CPU био процесор и када је већина рачунара имала само један CPU, није било нејасноћа.

Microsoft је изјавио да ће третирати сокет као један процесор.[13]

Oracle рачуна AMD X2 или Intel dual-core CPU као један процесор али има други начин бројања ја друге типове, посебно за процесоре са више од два језгра. IBM и HP рачунају мулти-чип модул као више процесора. Ако би мулти-чип модули бројали као један процесор, произвођачи CPU-а би имали подстицај да споје велике мулти-чип модуле па би њихови купци уштедели на софтверу.

Примери хардвера уреди

Комерцијални уреди

- Adapteva Epiphany, је више језгарна архитектура са до 4096 процесора на чипу

- Aeroflex Gaisler LEON3, вишејезгарни SPARC који постоји и у верзији отпорној да квар

- Ageia PhysX, вишејезгарна физичка процесорска јединица

- Ambric Am2045, 336-језгарни Massively Parallel Processor Array (MPPA)

- AMD

- A-Series, дво, тро, четворојезгарни Accelerated Processor Units (APU).

- Athlon 64, Athlon 64 FX и Athlon 64 X2 фамилија, двојезгарних десктоп рачунара

- Athlon II, дво-, тро-, четворојезгарни стони процесор.

- FX-Series, quad-, hex-, 8-језгарни стони процесор

- Opteron, дво-, тро-, четворо-, 8-, 12-, и 16-језгарни серверски/радне станице процесор.

- Phenom, дво-, тро-, четворојезгарни процесор.

- Phenom II, дво-, тро-, четворо-, честојезгарни стони процесор.

- Sempron X2, двојезгарни процесор улазног нивоа

- Turion 64 X2, двојезгарни лаптоп процесор

- Radeon и FireStream вишејезгарни GPU/GPGPU (10 језгара, 16 5-издаје широк суперскаларни стрим процесора по језгру

- Analog Devices Blackfin BF561, симетрични двојезгарни процесор

- ARM MPCore је потпуно синтетизован вишејезгарни контејнер за ARM11 MPCore and ARM Cortex-A9 MPCore процесорска језгра, намењен за високу перформансу уграђених апликација и апликација за забаву

- ASOCS ModemX, до 128 језгара, бежичана апликација

- Azul Systems

- Vega 1, a 24-језгарни процесор, пуштен 2005.

- Vega 2, a 48- језгарни процесор, пуштен 2006.

- Vega 3, a 54- језгарни процесор, пуштен 2008.

- Broadcom SiByte SB1250, SB1255 and SB1455.

- ClearSpeed

- CSX700, 192- језгарни процесор, пуштен 2008 (32/64-bit лебдећа тачка; Итеџер ALU)

- Cradle Technologies CT3400 и CT3600, оба вишејезгарна DSPs.

- Cavium Networks Octeon, a 16- језгарни MIPS MPU.

- Freescale Semiconductor QorIQ серије процесор, све до 8 језгара, Power Architecture MPU.

- Hewlett-Packard PA-8800 и PA-8900, двојезгарни PA-RISC процесор.

- IBM

- POWER4, први не-урађени двојезгарни процесор, пуштен 2001.

- POWER5, двојезгарни процесор, пуштен 2004.

- POWER6, двојезгарни процесор, пуштен 2007.

- POWER7, 4-, 6,-, 8- језгарни процесор, пуштен 2010.

- PowerPC 970MP, двојезгарни процесор, коришћен у Apple Power Mac G5.

- Xenon, тројезгарни, SMT-capable, PowerPC микропроцесор коришћен у Microsoft Xbox 360 играчкој конзоли.

- Kalray

- MPPA-256, 256-језгарни процесор, пуштен 2012 (256 usable VLIW cores, Network-on-Chip (NoC), 32/64-bit IEEE 754 compliant FPU)

- Sony/IBM/Toshiba's Cell процецор, деветојезгарни процесор са једном генералном употребом PowerPC језгро и осам специјализованих SPUs (Synergystic Processing Unit) оптимизованих за векторске операције које се користе у Sony PlayStation 3

- Infineon Danube, двојезгарни, MIPS-based, home gateway processor.

- Intel

- Atom, једни или двојезгарни процесор за netbook системе.

- Celeron Dual-Core, први двојезгарни процесор за буџет/основног нивоа

- Core Duo, двојезгарни процесор.

- Core 2 Duo, двојезгарни процесор.

- Core 2 Quad, 2 двојезгарна процесорска чипа пакована у вишечиповски модул.

- Core i3, Core i5, Core i7 and Octa Core фамилија вишејезгарних процесора, наследници Core 2 Duo и the Core 2 Quad.

- Itanium 2, двојезгарни процесор.

- Pentium D, 2 једнојезгарна чипа пакована у модул за више чипова

- Pentium Extreme Edition, 2 једнојезгарна чипа пакована у модул за више чипова.

- Pentium Dual-Core, двојезгарни процесор.

- Teraflops Research Chip (Polaris), a 3.16 GHz, 80-језгарни процесор прототип, за који је компанија прво изјавила да ће бити пуштен 2011.[14]

- Xeon дво-, четворо-, шесто-, осмо-, и 10-језгарни процесор.

- IntellaSys

- SEAforth 40C18, a 40- језгарни процесор [15]

- SEAforth24, a 24- језгарни процесорски дизајн од Charles H. Moore

- NetLogic Microsystems

- XLP, a 32-језгара, четири-нитиMIPS64 процесор

- XLR, an осам- језгара, четири-нитиMIPS64 процесор

- XLS, an осам- језгара, четири-нити MIPS64 процесор

- Nvidia

- GeForce 9 вишејезгарни GPU (8 језгара, 16 скаларни сптрип процесора по језгру)

- GeForce 200 вишејезгарни GPU (10 језгара, 24 скаларни сптрип процесора по језгру)

- Tesla вишејезгарни GPGPU (10 језгара, 24 скаларни сптрип процесора по језгру)

- Parallax Propeller P8X32, осмојезгарни микроконтролер.

- picoChip PC200 series 200–300 језгара по уређају за DSP & wireless

- Plurality HAL series тесно повани 16-256 језгара, L1 дељена меморија, хардверска синхронизација процесора.

- Rapport Kilocore KC256, a 257-језгарни микроконтролер са PowerPC језгрима и 256 8-bit "процесни елемент“.

- SiCortex "SiCortex node" има шест MIPS64 језгара на чипу.

- Sun Microsystems

- MAJC 5200, two-core VLIW processor

- UltraSPARC IV and UltraSPARC IV+, двојезгарни процесор.

- UltraSPARC T1, осмојезгарни, 32-нитни процесор.

- UltraSPARC T2, осмојезгарни, 64-истовремено-нитни процесор

- UltraSPARC T3, шеснаестојезгарни, 128- истовремено-нитни процесор.

- SPARC T4, осмојезгарни, 64- истовремено-нитни процесор

- SPARC T5, шеснаестојезгарни, 128- истовремено-нитни процесор

- Texas Instruments

- TMS320C80 MVP, петојезгарни мултимедија виоде процесор

- TMS320TMS320C66, 2.4.8 језгара dsp.

- Tilera

- TILE64, a 64-језгара 32-bit процесор

- TILE-Gx, a 100- језгара 64-bit процесор

- XMOS Software Defined Silicon четворојезгарни XS1-G4

Бесплатно уреди

- OpenSPARC

Академско уреди

- MIT, 16-језгара RAW Архивирано на сајту Wayback Machine (8. јун 2019) процесор

- University of California, Davis, Asynchronous низ једноставних процесора (AsAP)

- 36- језгара 610 MHz AsAP

- 167- језгара 1.2 GHz AsAP2

- University of Washington, Wavescalar процесор

- University of Texas, Austin, TRIPS процесор

Референце уреди

- ^ Suleman, Aater (20. 5. 2011). „What makes parallel programming hard?”. FutureChips. Архивирано из оригинала 29. 5. 2011. г. Приступљено 6. 3. 2013.

- ^ Vajda 2011, стр. 3.

- ^ Shrout, Ryan (2. 12. 2009). „Intel Shows 48-core x86 Processor as Single-chip Cloud Computer”. Архивирано из оригинала 14. 8. 2010. г. Приступљено 6. 3. 2013.

- ^ „Intel unveils 48-core cloud computing silicon chip”. BBC. 3. 12. 2009. Приступљено 6. 3. 2013.

- ^ Suleman, Aater (19. 5. 2011). „Q & A: Do multicores save energy? Not really.”. Архивирано из оригинала 16. 12. 2012. г. Приступљено 6. 3. 2013.

- ^ Multi-core in the Source Engine

- ^ AMD: dual-core not for gamers... yet

- ^ „Gamebryo's Floodgate page”. Архивирано из оригинала 16. 1. 2008. г. Приступљено 15. 12. 2013.

- ^ Ni, Jun. „Multi-core Programming for Medical Imaging” (PDF). Архивирано из оригинала (PDF) 1. 4. 2013. г. Приступљено 17. 2. 2013.

- ^ Merritt, Rick (6. 2. 2008). „CPU designers debate multi-core future”. EE Times. Приступљено 6. 3. 2013.

- ^ „Multicore packet processing Forum”. Архивирано из оригинала 21. 12. 2009. г. Приступљено 15. 12. 2013.

- ^ Darlinton, John; Ghanem, Moustafa; Guo, Yike; To, Hing Wing (1996), „Guided Resource Organisation in Heterogeneous Parallel Computing”, Journal of High Performance Computing, 4 (1): 13—23

- ^ „Multicore Processor Licensing[[Категорија:Ботовски наслови]]”. Архивирано из оригинала 2. 10. 2009. г. Приступљено 15. 12. 2013. Сукоб URL—викивеза (помоћ)

- ^ „80-core prototype from Intel”. Архивирано из оригинала 09. 11. 2006. г. Приступљено 15. 12. 2013.

- ^ „"40-core processor with Forth-based IDE tools unveiled"”. Архивирано из оригинала 24. 09. 2015. г. Приступљено 15. 12. 2013.

Литература уреди

- Vajda, András (2011). Programming Many-Core Chips. Springer. стр. 3. ISBN 978-1-4419-9739-5.

Види још уреди

Спољашње везе уреди